Floating point multiplication Multiplier vedic 2x2 Multiplier circuit

courses:system_design:synthesis:combinational_logic:example_of_a

Multiplier parallel proposed error composed

Floating point multiplication multiplier bit architecture basic figure

Block diagram of binary multiplierMultiplier operands two multiplied shifting Block diagram of an 8-bit multiplier.Multiplier array unsigned.

Booth multiplier array bitBlock-diagram of 4x4 ut multiplier Block diagram of 2x2 vedic multiplier.Block diagram of a complex multiplier[14].

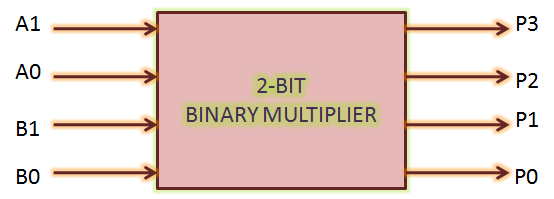

2 bit binary multiplier

Block diagram of the booth multiplier.Block diagram of the proposed multiplier with one parallel Booth's array multiplierBinary multiplier bit diagram block logic using two gates numbers figure vlsi multiplying.

The block diagram for the 2-bit multiplierMultiplier block diagram. Block diagram of the multiplier: two 8-bit operands a and b areMultiplier block.

Block diagram of the proposed multiplier

Multiplier vhdl bit logic diagram block example combinational synthesis courses system online .

.

![Block diagram of a complex multiplier[14] | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/profile/Hazry-Desa/publication/262067011/figure/download/fig1/AS:613910600237073@1523379101333/Block-diagram-of-a-complex-multiplier14.png)